当前位置:首页>>解决方案>Open RFSOC开源系统

发布时间:2023-07-28 18:34:39浏览次数:2572

随着新技术的发展,在电子系统领域底层硬件架构带来统一性的基础,彼睿电子作为RFSOC国内技术实际开发的领先者,在雷达、通信、电抗、测试测量、量子计算等领域积累了丰富的经验,在逐步取代传统分离式器件底层架构上面,给客户带来一种新的选择,新的技术应用是客户在产品性能,可靠性、高性价比上面带来了可喜回馈,彼睿电子适时推出OpenRFSOC开源系统。

OpenRFSOC框架是一个开源系统,可以更轻松地使用 AMD 自适应平台。提供基于 Python 、 Matlab、C++、GunRadio的接口来加载硬件覆盖和控制可编程逻辑,无需 ASIC 风格、以硬件为中心的设计工具。提供丰富的系统级、工程化、全开源的工程案列,主要面向雷达及电子对抗、无线通信、测试测量、量子计算等领域,持续不断更新开源案列,让工程师的相关开发,提供系统工程化的参考,极大降低系统工程化的研发门槛。

主要三方面心愿:

降低新技术RFSOC的使用成本

降低新技术RFSOC的开发难度

让工程师从底层硬件架构不一致,带来的反复底层开发种解脱出来

彼睿电子愿意联合知名高校和研究机构,针对于RFSOC开源系统,在统一的硬件架构和开发环境下,持续开发并且更新工程化、系统级、全开源功能案例,致力于学生在学习基础理论至实际具备完整功能的电子设备之间距离的缩小,让学生有个工程化、完整系统级功能案列,并且再次基础上,能够发挥学生天马行空的想象,实际开发出更具有创新功能的电子设备。

联合实验建立:

1、联合开发系统级工程化案列

2、教育培训

3、商业模式探讨

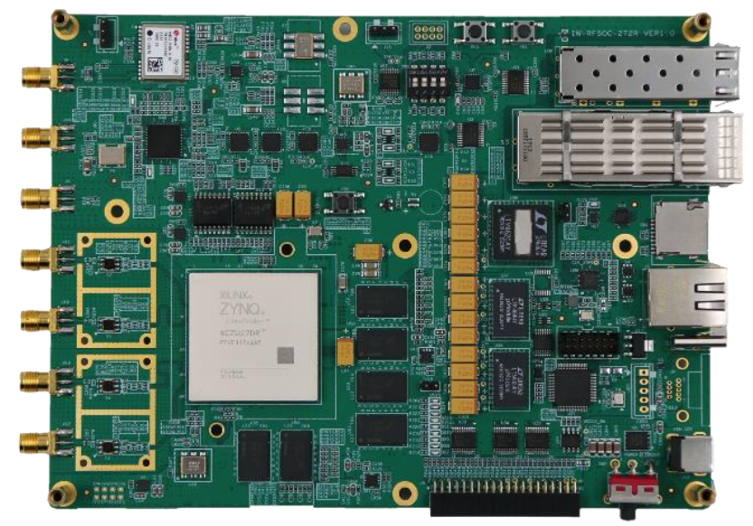

OpenRFSOC开源系统硬件板卡RFSoC 2x2 是一种高性能计算系统,针对高达 4 GSPS 的采样信号和高达 6 GSPS 的信号生成进行了优化。该板基于 AMD 的ZYNQ Ultrascale+ Gen1 RFSoC 设备,提供2个高速 ADC 端口、2个高速 DAC 端口、4GBytes 的 2400MHz DDR4 内存和一个用于高速数据卸载的 40G 以太网 QSFP28 端口。AMD ZYNQ UltraScale+ 设备包括一个四核 ARM Cortex-A53、一个双核 ARM Cortex R5F、单片直接射频采样 ADC 和 DAC,以及其他几个有助于获取和处理高速数据的高性能内核。RFSoC 板可与所有 AMD Vitis/Vivado 工具和PYNQ、Matlab、C++、GunRadio开源框架配合使用。

OpenRFSOC开源系统非实时开源软件架构

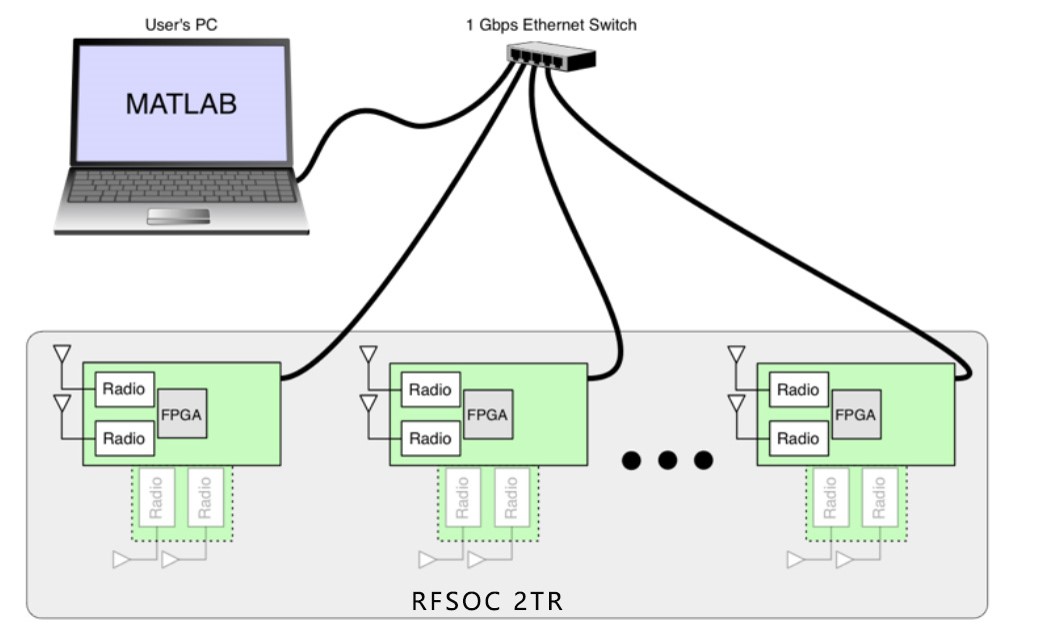

RFLab 框架的实现,允许构建和测试许多物理层设计。该参考设计结合了 RFLab 框架模块的 MATLAB 和 FPGA 实现,可轻松实现扩展和定制。虽然参考设计使用 MATLAB 来控制节点和执行信号处理,但它还允许具有严格延迟要求的应用程序将时间关键处理转移到 FPGA 中。

Matlab 案例

Ø 单音输出100MHz ~ 1GHz(matlab+HDL开源代码)

Ø 单音接收100MHz ~ 1GHz(matlab+HDL开源代码)

Ø 双音接收100MHz ~ 1GHz(HDL开源代码)

Ø 500MHz,1GHz 宽带matlab输出

Ø 500MHz,1GHz 宽带matlab接收

Ø 基本调制波形基带matab调制后直接输出

Ø 接收调制后的基带信号进行matlab处理

OpenRFSOC开源系统面向不同领域提供的系统级开源案列

无线通信领域

Ø 单发单收单载波400MHz带宽基带开源案列(HDL开源代码)

Ø 单发单收OFDM 400Mhz带宽基带开源案列(HDL开源代码)--规划案列

Ø 数字收音机AM/FM基带/FM广播(HDL开源代码)---规划案列

雷达及电子对抗领域

Ø 2TR LFM脉冲压缩(HDL开源代码)--规划案列

Ø 2T2R LFM AOA测角(HDL开源代码)--规划案列

Ø 数字信道化接收机(HDL开源代码)--规划案列

测试测量

Ø 具备接收2通道示波器(HDL开源代码、上位机控制软件代码开源)2TR板卡工程版本未裁剪移植完成

Ø 实时频谱分析仪/FFT(HDL开源代码、上位机控制软件代码开源)2TR板卡工程版本未裁剪移植完成

Ø 矢量信号源(HDL开源代码、上位机控制软件代码开源)2TR板卡工程版本未裁剪移植完成

电子工程底层基础开源工程案列

Ø MTS同步技术(HDL开源代码)

Ø 宽带幅相校准控制算法(HDL开源代码)--2TR板卡工程版本未裁剪移植完成